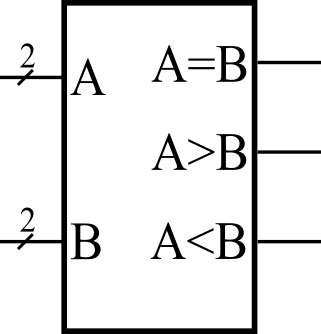

1、2、4、8という重みを持ったD/Aコンバータの各ビット出力と入力信号を比較して、各ビットのオン・オフを決めていきます。 最終的にはD/Aコンバータのコードが、変換データとなります。 図2 逐次比較型(SAR型)A/Dコンバータ このD/Aコンバータ部分は、最近では抵抗ラダーではなくコンデンサ・ラダーによるものが増えてきています。 このコンバータは次に2 ビットの2 進数x及び y を比較する比較器を設計する.ここでは,1 ビット比 較器を2つ用いて2ビット比較器を構成する.表2に2ビット比較器の真理値表を示す. ここで,出力(z ,,Lz)はx及び y の大小関係を表す出力である.図 2に ビットの比較 下表は、 8 桁の 2 進数について、 符号つき 2 進数と符号なし 2 進数を比較したものです。 符号つき 2 進数は最上位ビット (MSB most significan bit) が負の数を表し、 これを符号ビット (sign bit) といいます。 赤く表示しているのが符号ビットです。

芝杜uhd3000顶级4k蓝光高清hifi播放器体验 腾讯新闻

2bit 比較回路

2bit 比較回路-(a) ⼀般的なオペアンプの内部回路構成 入力段 利得段 出力段 入力端子 (in)入力端子 (in) 出力端子 (out) (a) ⼀般的なコンパレータの内部回路構成 out vee vcc inin 入力段 利得段 出力段 位相補償容量 (b) ba4558 内部等価回路 out vee vcc inin 入力段 利得段 出力段比較器とは入力された 2 個の数 a, b について、a が大きいか、等しいか、 b が大きいかを判定する回路である。 2bit の比較器が部品として使える場合に、それに機能を付加して3bit の比較器を構成しな

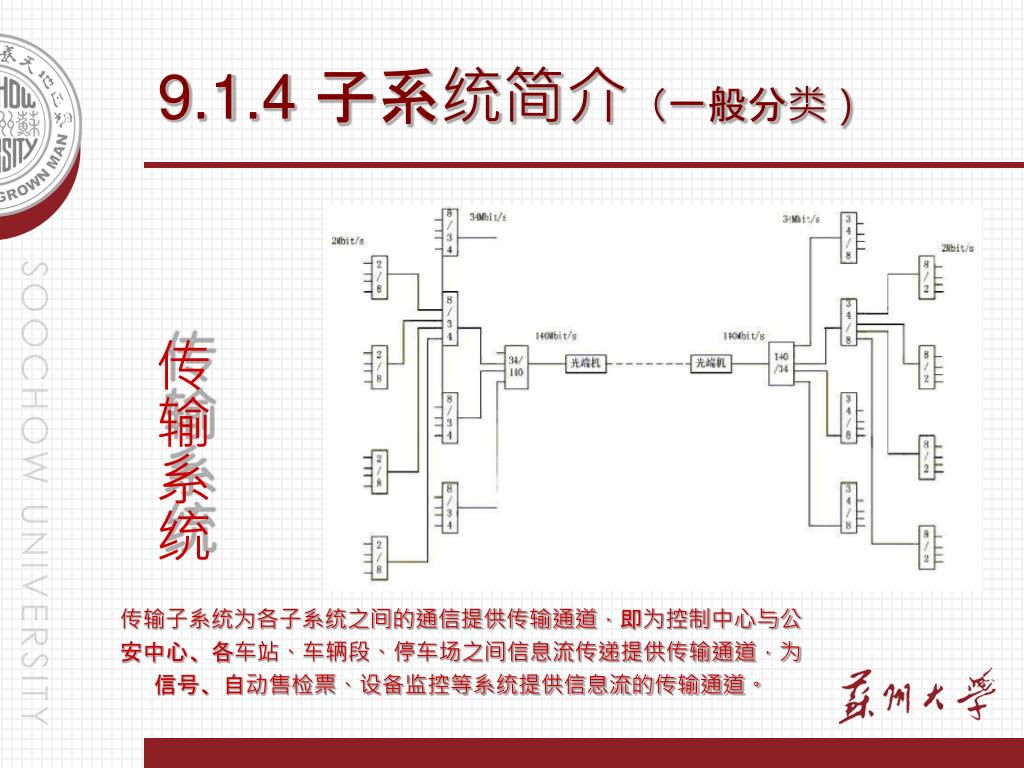

邏輯設計 Vhdl Verilog 計數器的設計考量 Fpga Hdl Counter Design Consideration 平靜的流域greenort Com 攝影創作與影像敘事

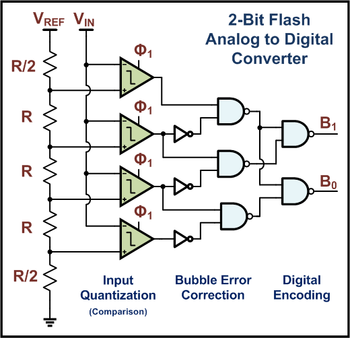

逐次比較型は1ビットごとに変換していくので変換回路は1回 路で済むが,多ビットのad 変換を行う場合にはビット分だけの サイクルを繰り返す必要があり時間がかかるようになる.これに 対して,多数のコンパレーターを並べて一気にad 変換を行おう回路構成は少し複雑 クロックはキャリーの伝播 遅延時間とffのスイッチング 遅延時間で決まる (非同期式より遅い) カウント値が安定する のに必要な時間が短い 出力にハザードが発生しない 用途 低速の回路 高い周波数のクロック の分周回路組み合わせ回路の設計と動作解析 31 25減算回路の設計 1)1Bit どうし(2Bit)の減算回路(半減算回路) 1Bit 減算回路のイメージ図 1Bit の減算例 00= 00 01= 11 10= 01 11=00 桁借り 1Bit の減算例を参考に1Bit の減算回路の真理値表を作成すると次のようになる。

比較器のオフセット電圧分布 LSB (4mV, 8b, 1Vpp) AC精度 ・サンプリングジッター ・入力容量による時定数と非線形容量 ・クロックと信号のタイミング分布(配線遅延) ・比較器の過渡特性 変換速度 ・比較器の応答(メタステーブル特性) ・ロジック系の速度Dffによる2bitレジスタの例(左図) ff出力は前もってクリア データa,b がck立ち上がりに同期して dffに読み込まれ記憶される 記憶されたデータはqa,qbよりパラレルに 出力 q d q >ck clr ck qa q d q >ck clr qb a b clr パラレル入力(pin) パラレル出力(pout) ffa ffb Weblio 辞書 > 辞書・百科事典 > 百科事典 > ΔΣ変調の解説 > ウィキペディア 索引トップ 用語の索引 ランキング カテゴリー ΔΣ変調 出典 フリー百科事典『ウィキペディア(Wikipedia)』 ( 0142 UTC 版) 脚注 ^ 安田靖彦「 巻頭言 技術の生みの親・育ての親 」 『郵政研究所月報』01年8月

組み合わせ回路の設計と動作解析 25 24加算回路の設計 1)1Bit どうし(2Bit)の加算回路(半加算回路) 加算回路 A B S (和) C (桁上げ) 1Bit 加算回路のイメージ図 1Bit の加算例 00= 00 01= 01 10= 01 11=10 桁上がり 1Bit の加算例をもとに真理値表を作成する。 1Bit 加算の真理値表論理回路基礎 摂大・鹿間 加算時間遅れ解消:ルックアヘッドキャリー方式 リプルキャリー方式の時間遅れ解消 下位の全ての桁上がりを前もって演算し、その桁に加算 Look ahead carry (先見桁上げ)方式 桁ごとに、専用の桁上がり演算回路(C0, C1, ・・・)を有す比較器 2bit の比較器とは,2bit 数A(= 2a1 a0), B(= 2b1 b0) を比較し • A > B ならz1 = 1, z2 = 0 • A < B ならz1 = 0, z2 = 1 • A = B ならz1 = 1, z2 = 1 となるようz1, z2 を出力するものである。z1 とz2 の真理値表と,z1 に関するカルノー・ マップは以下の通りである。 比較器の真理値表

Flash Adc 原理flash Qhcoh

邏輯設計 Vhdl Verilog 計數器的設計考量 Fpga Hdl Counter Design Consideration 平靜的流域greenort Com 攝影創作與影像敘事

Dac 基本形2(バイナリ方式) そのままデジタル値を受けて動作する回路方式をバイナリ方式と呼びます。 抵抗使用の場合のバイナリ方式は、回路構成によりデータに重み付けを持たせたもので、代表例としてr2rラダー回路があります。 キャパシタ使用の場合のdacは、スイッチを切り替えながら組合せ回路の設計 比較器(1) 正の2進データの比較 ( ) ( ) 1 0 1 0 B b b b A a a a n k n k "" "" − − = = A≥B B :1を出力 (例) A< :0を出力る場合の回路例をもとに、2電源レベルシフタic を使用した場合とワンゲートロジックic を使用した場合で比較を行いま す。and回路と電圧レベル変換が必要な場合の回路例を図221に示します。 図 221 and回路と電圧レベル変換が必要な回路例

Http Www Phelipu Com Tw Download Delta mh300 High Um Tc Pdf

Http Ir Lib Ncut Edu Tw Bitstream 4943 2 E6 96 B0 E5 8f E6 E5 90 E5 9e 8b E6 9e B6 E6 8bpwm E6 99 B6 E7 87 E8 A8 Ad E8 A8 E8 87 E5 Af A6 E7 8f Be Pdf

計算モード切り替え 3bit程度 1bit ALUはn bit ALUとして接続することを前提としているため、繰り上がり用のピンが存在します。もちろん、繰り上がりが発生するのは加減算の場合のみです。このページでは、コンパレータ(比較器)の動作を理解します。 前のページで学んだ抵抗分圧に加えてコンパレータを理解できれば、矩形波発生回路(方形波発生回路)の理解に大きく近づきます。 1 コンパレータ(比較器)の動作 コンパレータ(比較器)は、2つの電圧を比較するために用いられます。 コンパレータ(比較器)はオペアンプを用いることで実現もちろんすべての論理回路について、ここで触れることはできないので、簡単で基本的な回路を触れるだけにしよう。 まずは、複数の入力信号の大小を比較し、その結果を出力する機能を持った回路である「 比較回路 (comparator)」について見てみることにしよう。 比較回路は二つ以上の多入力だが、今回は最も簡単な「2入力・3出力」について扱う。 ・比較回路

Cnb 一种周期性信道状态信息的发送方法及系统 Google Patents

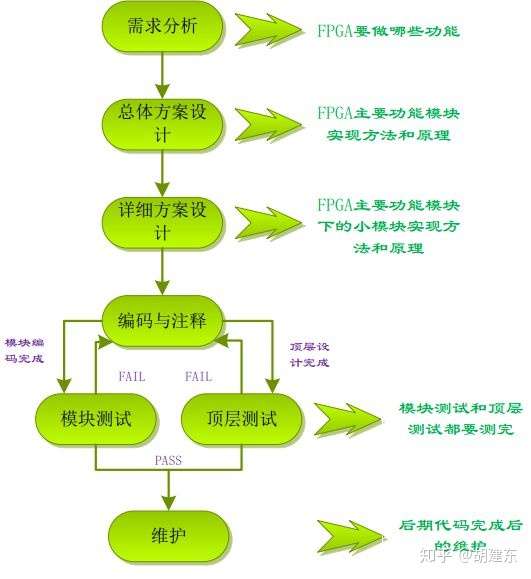

Vlsi设计快速指南 Vue教程

大小比較ですか?二ビットならたぶんパラレルに比較でしょう。 上の桁を比較、違えばそれが結果、同じなら下の桁の比較が 結果になります。つまり一ビットの比較が二つとどの結果を 使うかの判断回路があれば済みます。Nビット比較器 組合せ回路の設計 a0 =0,b0 =1Þ f0 =1 f0 =a0b0 fn b0 b1 a1 a0 CMP b2 a2 bn an CMP ・・・ CMP Ritsumeikan OCW多ビット比較器の場合 比較器のビット数と出力の組み合わせ数 1 1ビット 21×21 = 4通り 2 2ビット 22×22 = 16通り 3 3ビット 23×23 = 64通り 4 4ビット 24×24 = 256通り ビット数が増えるにつれ膨大な組み合わせが必要 5 5ビット 25×25 = 1024通り

Www Lhu Edu Tw M Admission Publish Publish 17 02 E8 98 87 E6 99 Af E6 9a E4 Bf E7 94 A8simulink E8 94 E5 8a E8 A8 Ad E8 A8 E5 8a 9f E7 8e 87 E5 9b A0 E7 B4 A0 E4 Bf Ae E6 Ad A3 E9 9b E8 Af Pdf

榮耀發佈5g手機新品 吿別 半斤機 從 輕 出發 森早資訊

4 農業機械学実験i 電子回路設計編第3版 33 andゲート(論理積) 2つ以上の入力がすべて1のとき出力が1となる.2入力の場合の真理値表を表3に示す.3入力以 上に関しても同様に入力のうちひとつでも0があれば,出力は0となる. 表3 andゲート(2入力)の真理値表少した。図10,図11に従来回路と提案回路のVoutでのリッ プルを示す。提案回路では従来回路よりリップルが増大し たが提案回路のリップルはmVppでありVoutの51Vに 対して約004%と非常に小さい。 次に、従来回路と提案回路の過渡応答特性を比較して示 す。を考えたもので半加算器を2つとor 回路でも表現できる。この回路を考え て真理値表を書く。 上の全加算器と半加算器を用いて2 ビットの加算が行える回路を考えて真 理値表を書く。 求めた真理値表から加法標準形に直すことで論理関数を求める。

野良のブログ 16

Http Www Hycontek Com Wp Content Uploads Apd Sd Tc Pdf

複数ビット加算回路 先頭へ 半加算回路 2進数の加算を行うための、最下位ビットの加算; 電子回路ドリル III(5) MONOist 問題5 シミュレータでVerilog HDLを動かそう : 完全マスター! 電子回路ドリル III(5) » 08年10月02日 00時2 同期式カウンタの構成法 21 同期式カウンタの例 はじめに、 最も簡単な同期式カウンタの例 を示します。 クロックの立ち上りで出力 q が反転 し、 (0→1→2→3→0→1) のようにカウントします。 エッジトリガーdffを2個用いている点は、 非同期式の4進カウンタと同じ ですが、

单片机 Mcu加油站

4d F736f F D c6a6ecc5debfe8b35dad70bb50b9eab2dfb3f8a769abcaadb1 Pdf 免费下载

AND回路からAND関数へ 関数への入力は2つあり、それぞれの値を受け取る変数(引数)を A,B とする.また、関数の出力はreturnを使う. Logisimで組み合わせ回路(Combinational Logic)の比較回路(Comparatorコンパレータ)を学んでいきます。比較回路は、単純に2つの入力を比較して、その状態を出力します。 ひと桁の二進数の入力Aを考えると0か1です。 入力A 0 1シミュレーションにより次の回路の動作を確認する: and, or, exor ゲートを用いて半加算器,および,全加算器のそれぞれを 1つ構成し, それらを組み合わせて,2進2ビットの加算回路を作成せよ. 作成した回路はシミュレーションにより動作を確認すること.

10 号 nビット比較回路 Astamuse

4 組合せ回路 Digital Electronic Circuits 1 0 ドキュメント

2ビット比較器の論理関数 y1 y0 x1 x0 0 0 0 ==> 1 0 >> x >y • = x =y • < x出力ビット 2bit 計算結果 1bit;第4章 階層回路図の作成法 (4bit 加算回路の例) 本章では、 4bit加算回路の作成を通して、NSDrawでの階層回路の作成方法を学びま す。 4.1 回路シンボル(インバータ)の作成 4.2 2入力 NAND ゲートの作成 4.3 2入力 XOR ゲートの作成 4.4

比較回路 石丸技術士事務所 ディジタル技術資料

資深fpga 老司機 設計精華總結 壹讀

論理回路は大きく組み合わせ論理回路(combinational circuit)と順序論理回路(sequential circuit)の2 つに分けられます。 組み合わせ回路 内部には状態を持たず、現在の入力だけで出力が決まるような回路• 回路が簡単 • 桁上げ伝搬に時間がかか る ci0 ci0 x0 y0 s0 co0 fa0 ci1 x1 y1 co1 fa1 cin−1 xn−1 yn−1 fan−1 con−1 s1 sn−1 con−1 x y s x = (xn−1,x1,x0)2等と定義 教科書p174 図614より 16し入力と比較するので,回路は簡単で低電力であるが, 原理的に変換速度は遅い. Pipe方式も逐次比較であるが,時系列データに対して パイプライン並列動作する.回路規模はパイプライン 段数に比例して増加するが,高速変換が可能である.

Ppt C 9 C Aÿza E E Aº E S E Sa A Za A Powerpoint Presentation Id

57行星减速步进电机 4种直流电机控制电路详解 含图含公式 直观又细致 不懂都难 深圳市踢踢电子有限公司www 58motor Com

符号化信号をもとの信号に戻す回路をデコーダ(decoder,復号化器)と呼ぶ 2ビット・エンコーダ 1が入力された端子の番号を2進数2ビットの信号として出力するアナログ技術シリーズ アナログ集積回路 Ⓒ05 Gunma Industry Support Organization 15 従来型AD変換器(逐次比較型)原理図 前置フィルタ 荒い特性の フィルタ 高精度 フィルタ 信号帯域 fн/2 fs/2 fн/2 fн fs 比較器 DA変換器 逐次比較 レジスタ デジタル 信号処理補間回路周波数特性比較 50Ωドライブを仮定 補間小 SNR悪化 ENOB 6bit 56bit 52bit 0M 400M 600M 800M 有効信号帯域 3dB 2bit補間 1bit補間 補間無し SNDR 38dB 36dB 34dB 0M 400M 600M 800M 0M 400M 600M 800M SNR 38dB 37dB 36dB 35dB 補間大 THD悪化 THD 0M 400M 600M 800M50dB40d0dB

02 号 大小比較回路 Astamuse

Adc采样的值跳动 嵌入式er必知 模数采样知多少 最全总结 一只御姐姐的博客 程序员宅基地 程序员宅基地

1 ビット比較器を利用して次に複数ビット比較器を実現する。例として 2 ビット比較器を取り上げる。 この回路は入力された 2 ビットの2進数 a1,a0 と b1,b0 の大小関係を判定する。 a1, b1 が上位桁になる。真理値表は次のようになる。

资深fpga 老司机 设计精华总结 知乎

Http Www Calip Com Tw Downloads Support 17 6 Pdf

Http Chur Chu Edu Tw Bitstream 2548 1 Nc092chpi Pdf

dbcd 8421 1 2 B 1 B

採用dac 比較器架構代替集成adc輕鬆解決應用共性問題 模擬技術 快遞國內 快遞國內

Www Pochin Com Tw Templates Cache 5452 Images 50bab2805 Pdf

Http Www Teanlift Com Upload 18 05 Ce Pdf

Data Sheet

Cnb 一种周期性信道状态信息的发送方法及系统 Google Patents

Www Pochin Com Tw Templates Cache 5452 Images 50bab2805 Pdf

Cnb 一种基于多模干涉耦合器的硅基光子模数转换器 Google Patents

Www Info Kindai Ac Jp Lc Lecture Logiccircuits05 Pdf

4d F736f F D c6a6ecc5debfe8b35dad70bb50b9eab2dfb3f8a769abcaadb1 Pdf 免费下载

4 組合せ回路 Digital Electronic Circuits 1 0 ドキュメント

荣耀v40轻奢版评测 66w快充 超曲屏性能均衡的轻旗舰机 手机

图 4种直流电机控制电路详解电机控制专区电路图维库电子市场网

计算机科学 光怪陆离前端

Sde P伺服驅動器說明書 V1 01 02

Web Hocom Tw Uploads Userfiles Files 6zrev5r27z8tr0r Pdf

4種直流電機控制電路詳解 不懂都難 每日頭條

P4 17 2bit比較器配合de2 70修改後程式 Alex9ufo 聰明人求知心切

Ad1376 Ad1377是高分辨率的16位模拟 数字转换器

Http Www Etop Org Tw Index Php C Adm M Getreportfile D Adm I

2

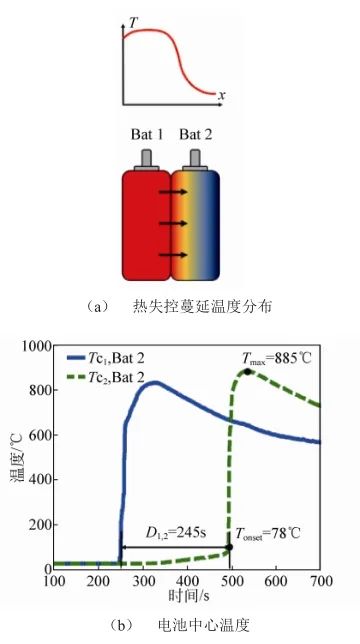

锂离子电池热失控蔓延研究进展 行业动态 广州市绿原环保材料有限公司

德力西delixi 微型断路器dz47p 1p N 10a C型dz47pc10 正天牛工业官方商城

Http Web Nihs Tp Edu Tw Ezfiles 1 1001 Img 28 Pdf

Www Eaton Com Content Dam Eaton Products Industrialcontrols Drives Automation Sensors Variable Frequency Drives China Powerxl Df1 User Guides E4 8a E9 A1 Bf powerxl df1 E4 Ba E5 93 81 E6 8b E5 86 8c Pdf

Fps 用户手册

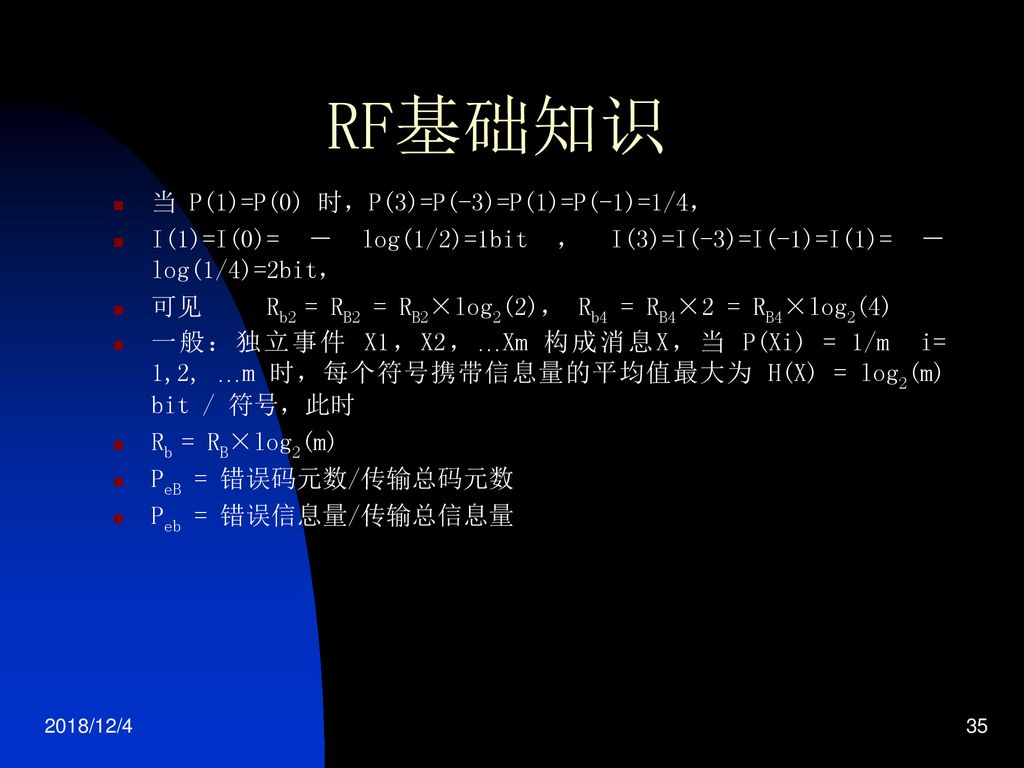

射频系统知识生产技术部 郑长瀚18 12 4 Ppt Download

Grl100 711p Chinese 6f2s0918 1 0

Cn0337 参考电路 亚德诺半导体

Www Rgbautomatyka Pl En P File 6e64b377ee6bee2d75c3c1ac76d5cc M3 Klawiatura Membranowa Cnc Mitsubishi Manual Pdf

4d F736f F D c6a6ecc5debfe8b35dad70bb50b9eab2dfb3f8a769abcaadb1 Pdf 免费下载

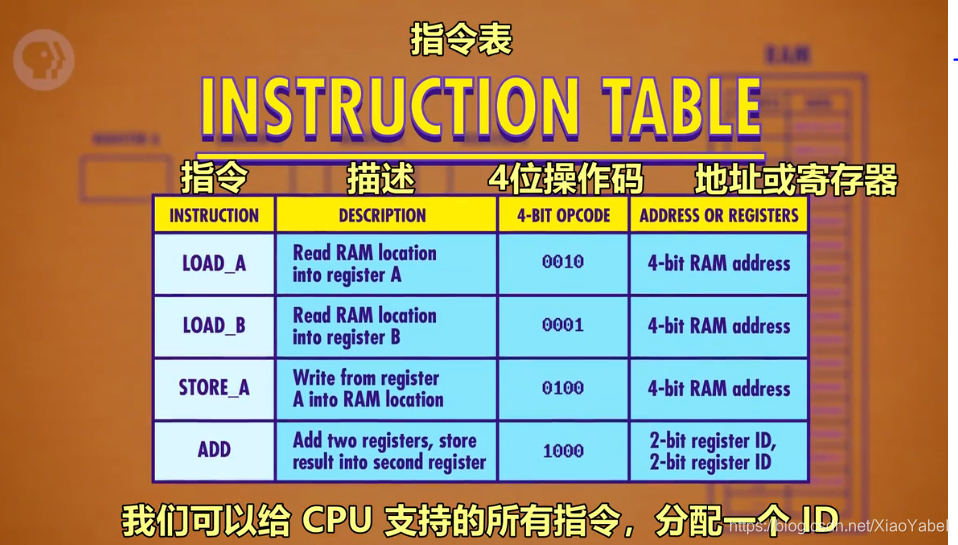

计算机基础 计算机科学速成课 Xiaoyabei的博客 Csdn博客 计算机科学速成课

Http Chur Chu Edu Tw Bitstream 2548 1 Nc092chpi Pdf

资深fpga 老司机 设计精华总结 开源block

紫光同创国产fpga教程 第十章 Ddr3读写测试实验 知乎

2

面试分享 一 Java知识 一只病猫

Cn0337 参考电路 亚德诺半导体

Http 163 19 9 241 Ischool Public Resource View Open Php File df6cc343a49c1732ff9a8a654 Pdf

现场总线控制系统 Fcs 与集散控制系统dcs的区别 现场总线 电工学习网

Hope Auto Com Downfile Php Flang Tw Id Type Dnpag

潘时龙教授 微波光子雷达及关键技术 下 光电汇

请教 Z Stack3 0 2 Znp的应用 Zigbee 和thread 论坛 Zigbee 和thread E2e 设计支持

几种功能电路的bit测试方案设计及其仿真 项菁还 新浪博客

真理値 Truth Value Japaneseclass Jp

Http Ir Hust Edu Tw Dspace Bitstream 26 1 E5 85 A8 E6 96 87 Pdf

模拟集成电路设计与仿真 何乐年 08 Pdf

使用模拟pid控制器测量直流电动机的位置和速度控制 电机控制 电子技术论坛 广受欢迎的专业电子论坛

Ppt Mixed Signal Ic Design Powerpoint Presentation Free Download Id

Ppt Mixed Signal Ic Design Powerpoint Presentation Free Download Id

课程网页 Ppt Download

t如何制作流程图 你肯定不知道 雅思写作流程图原来可以这么简单 还是那个小宇的博客 程序员宅基地 程序员宅基地

4d F736f F D c6a6ecc5debfe8b35dad70bb50b9eab2dfb3f8a769abcaadb1 Pdf 免费下载

2

芝杜uhd3000顶级4k蓝光高清hifi播放器体验 腾讯新闻

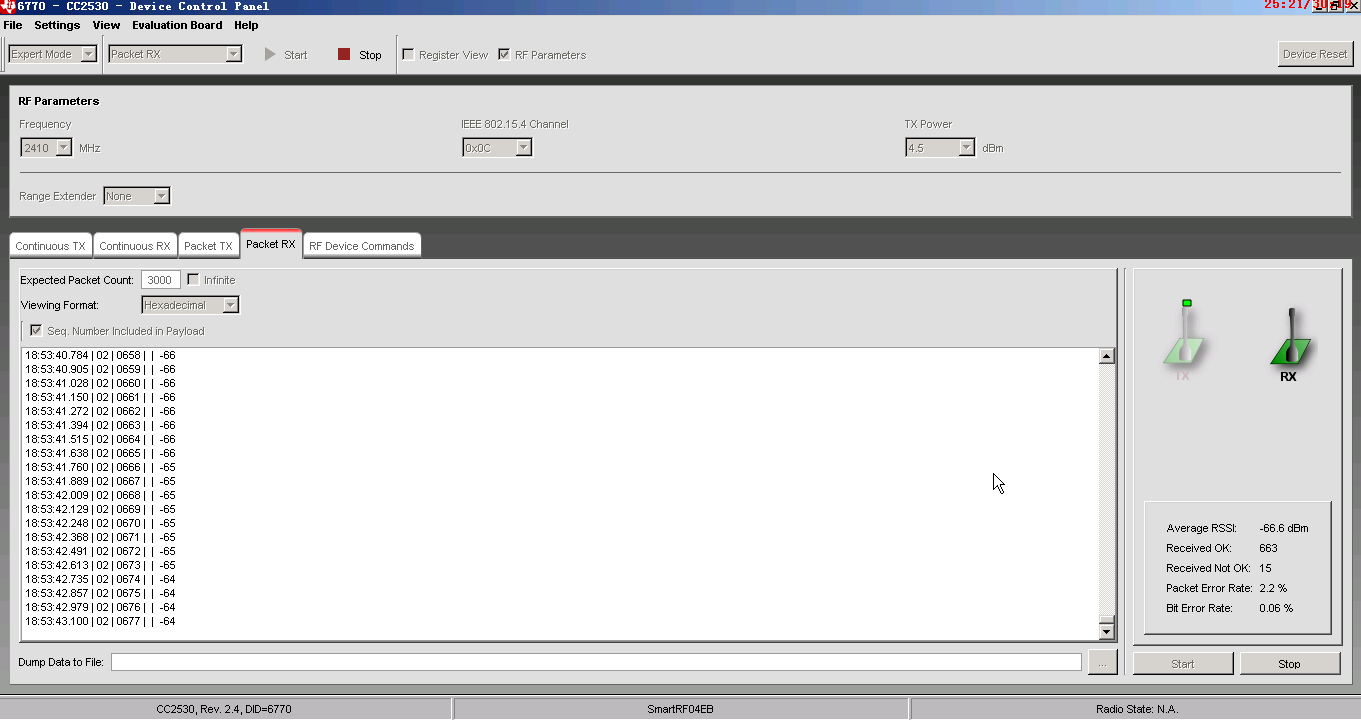

01 Ti Cc2530的io口控制 Jklinux的博客 程序员宅基地 程序员宅基地

Keil Software Cx51 编译器用户手册中文完整版 403页

Http Chur Chu Edu Tw Bitstream 2548 1 Nc092chpi Pdf

Can Bus系统 汽车维修技术网

Pke智能钥匙系统工作原理详解

技术 Mcu加油站

4412开发板linux开发指南9 公司新闻 友坚科技 全面的产品选择及专业化的量身定制解决方案

2

Pdf Development And Challenges Of Synthetic Genetic Circuits

2

A E A ƒae ºa A E E

15 11 07 Adf435x 頻率合成器概述 黎煥欣的工作部落格 痞客邦

4 組合せ回路 Digital Electronic Circuits 1 0 ドキュメント

nビット比較回路

Http Www Etop Org Tw Index Php C Adm M Getreportfile D Adm I

Dali协议了解 Makeryzx的博客 Csdn博客 Dali协议

Http Www Jdzj Com Userdocument 15a Dglyjd Document Pdf

Mcal Spi Module原理和配置详解 面包板社区

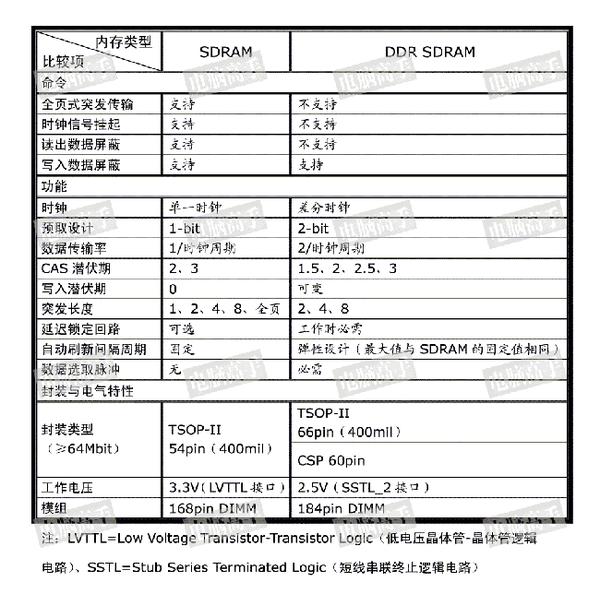

Ddr2基础知识 Angu66的博客 Csdn博客

論理回路の問題です 2つの2ビットの入力と3つの出力を持つ2ビット比較 Yahoo 知恵袋

Serdes 相关 程序员大本营

乾貨分享hybrid音頻的基礎 數字比特與動態的關係 每日頭條

0 件のコメント:

コメントを投稿